采用多功能器件实现新型数字信号中和器的应用电路设计及数据处理与存储策略

随着数字信号处理技术的飞速发展,对信号质量的要求日益提高,尤其在复杂电磁环境或存在强干扰源的场景下,如何有效“中和”或抑制非期望信号成分,成为关键挑战。本文探讨一种采用多功能器件实现的新型数字信号中和器的应用电路设计,并阐述其配套的数据处理和存储策略。

一、 新型数字信号中和器的设计理念

传统的中和或滤波技术多采用分立元件或专用集成电路,在灵活性、集成度和可重构性方面存在局限。本文提出的新型数字信号中和器,其核心在于利用现场可编程门阵列(FPGA)或高性能数字信号处理器(DSP)等可编程多功能器件作为处理核心。这些器件集成了逻辑单元、存储块、高速接口和算术模块,能够实现复杂的自适应算法,实时识别并生成与干扰信号幅度相等、相位相反的“中和信号”,从而在数字域实现对目标信号的“净化”。

二、 应用电路设计

电路系统主要由信号采集、核心处理、信号重建及控制接口四部分组成。

- 信号采集模块:采用高速模数转换器(ADC)将输入的含噪模拟信号转换为数字信号。设计中需重点考虑ADC的采样率、分辨率与后续处理带宽的匹配,并做好前端抗混叠滤波与信号调理。

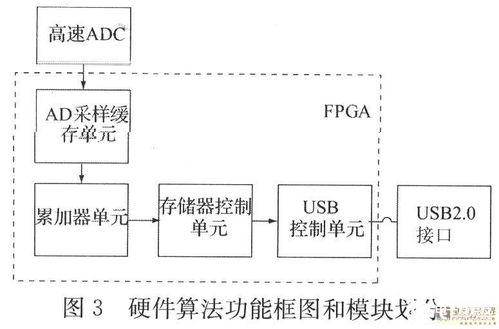

- 核心处理模块(多功能器件):这是设计的核心。在FPGA或DSP内部,设计实现以下关键单元:

- 干扰分析与特征提取单元:通过快速傅里叶变换(FFT)或小波变换等算法,实时分析信号频谱,识别干扰信号的频率、幅值与相位特征。

- 自适应中和算法引擎:采用最小均方(LMS)或递归最小二乘(RLS)等自适应算法,动态计算并生成最优的中和信号系数。该算法在多功能器件的并行处理架构上能高效执行。

- 数字信号合成单元:根据算法引擎输出的系数,实时合成数字形式的中和信号。

- 信号重建模块:将原始输入信号与生成的中和信号在数字域进行实时相加(即相消),得到“纯净”的目标信号,再经由数模转换器(DAC)输出为模拟信号。

- 控制与接口模块:利用多功能器件上的嵌入式处理器(如FPGA中的软核)或外接微控制器,管理系统参数配置、工作状态监控,并提供如UART、SPI、Ethernet等接口与上位机通信,实现算法的远程更新与参数调整。

三、 数据处理与存储策略

高效的数据处理与可靠的存储是保障系统性能的关键。

- 实时数据处理流程:

- 流水线架构:在FPGA设计中,采用深度流水线技术处理ADC来的高速数据流,确保信号采集、特征分析、系数计算、信号合成与相消等环节无缝衔接,满足实时性要求。

- 并行计算优化:充分利用DSP的多核心或多FPGA的并行处理能力,将宽带信号分割为多个子带并行处理,大幅提升整体处理速度。

- 定点与浮点运算权衡:根据精度与资源消耗需求,在多功能器件中合理分配定点与浮点运算单元,在保证算法性能的同时优化资源利用率。

- 数据存储机制:

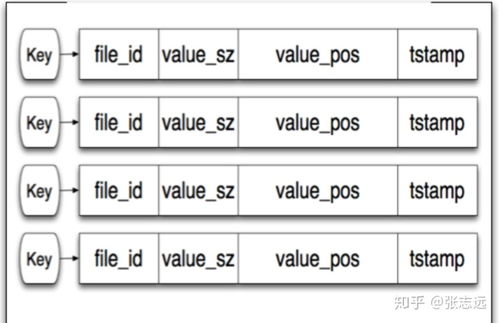

- 片上存储:利用多功能器件内部的Block RAM或分布式RAM,作为算法运算过程中的高速缓存,存储中间变量、滤波器抽头系数、当前帧的信号数据等,实现极低延迟的数据交换。

- 外部存储扩展:为支持长时间工作、历史数据回溯或复杂算法所需的庞大数据集,可通过控制器连接外部DDR SDRAM或Flash存储器。例如,将一段时间的原始信号与处理后信号同步存储,用于后续的离线分析和算法优化。

- 非易失性参数存储:将系统配置参数、校准系数、最优算法参数等关键信息存储于外部的EEPROM或Flash中,确保系统上电后可快速恢复至最佳工作状态。

四、 应用前景与

采用多功能器件实现的新型数字信号中和器,具有设计灵活、性能可升级、易于集成等突出优点。其应用电路结合了高速数据转换、可编程实时处理和智能算法,而配套的数据处理与存储策略则确保了系统的效率与鲁棒性。该设计可广泛应用于无线通信、雷达系统、医疗电子、音频处理等领域,有效提升设备在复杂环境下的信号接收质量与可靠性,具有重要的实用价值和广阔的发展前景。未来的工作可聚焦于更智能的算法(如基于机器学习)、更高集成度的片上系统(SoC)设计以及更低的功耗优化。

最新产品

SQL Server存储过程插入50万测试数据缓慢问题剖析与存储引擎优化浅谈

SQL Server中存储过程、触发器、事务处理及数据处理与存储务综合应用

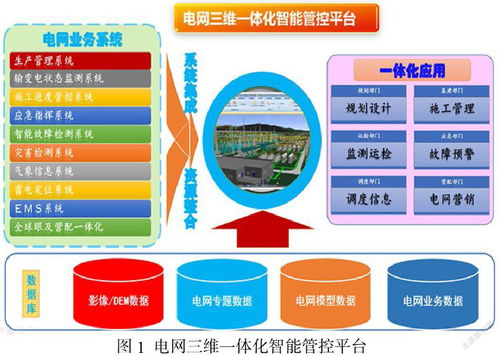

电网调控运行大数据存储与处理技术的应用策略

智慧工地系统赋能南京宁一 高效数据处理与存储之道

大数据数仓建设实战 DWD与DIM层数据准备、分层职能与日志处理详解

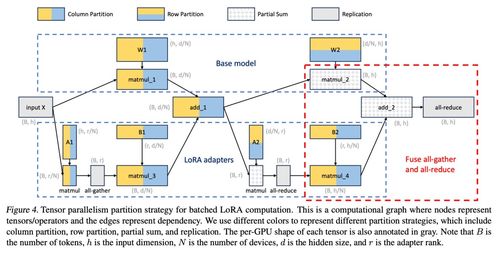

单GPU运行数千大模型 UC伯克利提出全新微调方法S-LoRA,革新数据处理与存储范式

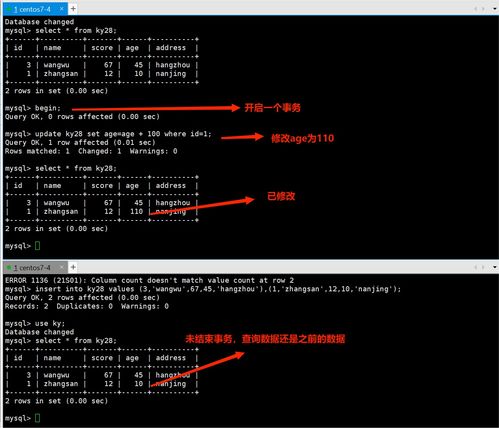

MySQL数据库事务与存储引擎 数据处理与存储的基石

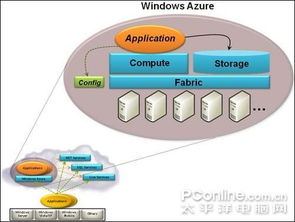

云中漫步 透视 Windows Azure 数据处理与存储服务原理

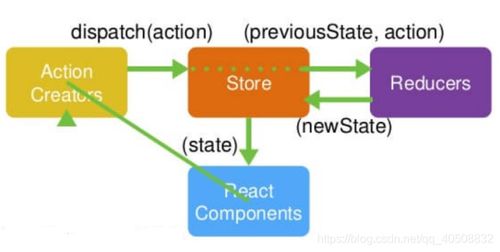

深入理解Redux 核心概念与数据处理实践指南

Web 3.0 数据处理与存储夯实基础,静待应用生态爆发